# Integrated Analog Front-End for Pulse Oximeters

Check for Samples: AFE4490

# FEATURES

- Fully-Integrated Analog Front-End for Pulse Oximeter Applications:

- Flexible Pulse Sequencing and Timing Control

- Transmit:

- Integrated LED Driver (H-Bridge or Push/Pull)

- 110-dB Dynamic Range Across Full Range (Enables Low Noise at Low LED Current)

- LED Current:

- Programmable Ranges of 50 mA, 75 mA, 100 mA, 150 mA, and 200 mA, Each with 8-Bit Current Resolution

- Low Power:

- 100 µA + Average LED Current

- LED On-Time Programmability from (50 μs + Settle Time) to 4 ms

- Independent LED2 and LED1 Current Reference

- Receive Channel with High Dynamic Range:

- Input-Referred Noise: 13 pA<sub>RMS</sub> (0.1-Hz to 5-Hz Bandwidth)

- 13.5 Noise-Free Bits (0.1 Hz to 5 Hz)

- Analog Ambient Cancellation Scheme with Selectable 1-µA to 10-µA Ambient Current

- Low Power: < 2.3 mA at 3.0-V Supply</p>

- Rx Sample Time: 50 µs to 250 µs

- I-V Amplifier with Seven Separate LED2 and LED1 Programmable Feedback R and C Settings

- Integrated Digital Ambient Estimation and Subtraction

- Integrated Fault Diagnostics:

- Photodiode and LED Open and Short Detection

- Cable On/Off Detection

- Supplies:

- Rx = 2.0 V to 3.6 V

- Tx = 3.0 V or 5.25 V

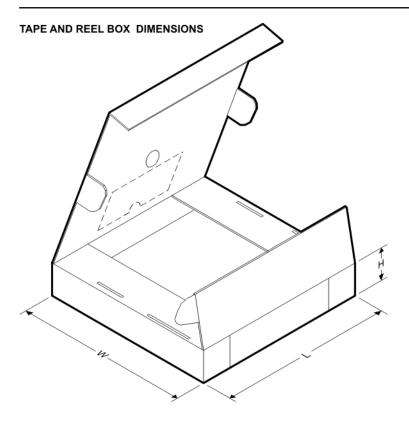

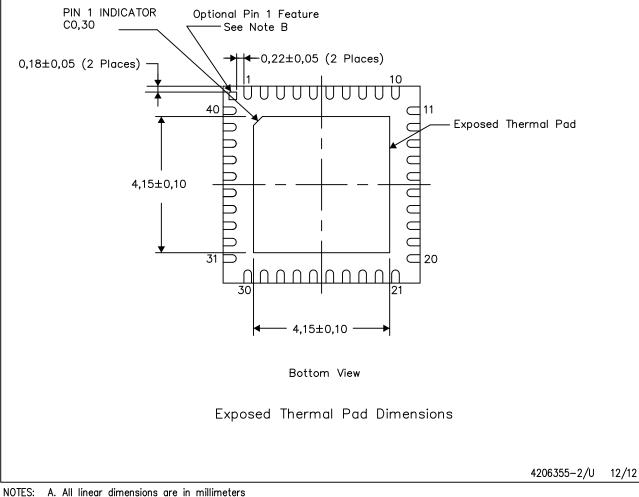

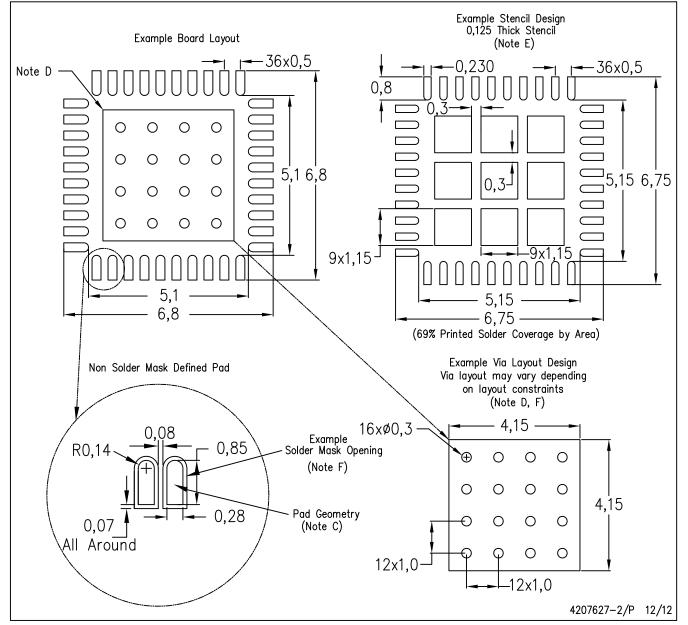

- Package: Compact QFN-40 (6 mm × 6 mm)

- Specified Temperature Range: –40°C to +85°C

# APPLICATIONS

- Medical Pulse Oximeter Applications

- Industrial Photometry Applications

# DESCRIPTION

The AFE4490 is a fully-integrated analog front-end (AFE) that is ideally suited for pulse-oximeter applications. The device consists of a low-noise receiver channel with a 22-bit analog-to-digital converter (ADC), an LED transmit section, and diagnostics for sensor and LED fault detection. The AFE4490 is a very configurable timing controller. This flexibility enables the user to have complete control of the device timing characteristics. To ease clocking requirements and provide a low-jitter clock to the AFE4490, an oscillator is also integrated that functions from an external crystal. The device communicates to an external microcontroller or host processor using an SPI<sup>™</sup> interface.

The AFE4490 is a complete AFE solution packaged in a single, compact QFN-40 package (6 mm  $\times$ 6 mm) and is specified over the operating temperature range of -40°C to +85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SPI is a trademark of Motorola.

All other trademarks are the property of their respective owners.

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| FAMILY AND ORDERING INFORMATION |        |                            |                                |                     |                                   |  |  |  |

|---------------------------------|--------|----------------------------|--------------------------------|---------------------|-----------------------------------|--|--|--|

| PRODUCT PACKAGE-LEAD            |        | LED DRIVE<br>CONFIGURATION | LED DRIVE CURRENT<br>(mA, max) | POWER SUPPLY<br>(V) | OPERATING<br>TEMPERATURE<br>RANGE |  |  |  |

| AFE4490                         | QFN-40 | Bridge, push-pull          | 50, 75, 100, 150, and 200      | 3 to 5.25           | –40°C to +85°C                    |  |  |  |

| AFE4400                         | QFN-40 | Bridge, push-pull          | 50                             | 3 to 3.6            | 0°C to +70°C                      |  |  |  |

## FAMILY AND ORDERING INFORMATION

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                             |                                                                              | VALUE                    | UNIT |

|-----------------------------|------------------------------------------------------------------------------|--------------------------|------|

| AVDD to AVSS                |                                                                              | -0.3 to +7               | V    |

| DVDD to DGND                |                                                                              | -0.3 to +7               | V    |

| AGND to DGND                |                                                                              | -0.3 to +0.3             | V    |

| Analog input to AVSS        |                                                                              | AVSS – 0.3 to AVDD + 0.3 | V    |

| Digital input to DVDD       |                                                                              | DVSS – 0.3 to DVDD + 0.3 | V    |

| Input current to any pin ex | cept supply pins <sup>(2)</sup>                                              | ±7                       | mA   |

| la mut au ma at             | Momentary                                                                    | ±50                      | mA   |

| Input current               | Continuous                                                                   | ±7                       | mA   |

| Operating temperature range |                                                                              | -40 to +85               | °C   |

| Storage temperature range   | e, T <sub>stg</sub>                                                          | -60 to +150              | °C   |

| Maximum junction tempera    | ature, T <sub>J</sub>                                                        | +125                     | °C   |

| Electrostatic discharge     | Human body model (HBM)<br>JEDEC standard 22, test method A114-C.01, all pins | ±1000                    | V    |

| (ESD) ratings               | Charged device model (CDM)<br>JEDEC standard 22, test method C101, all pins  | ±500                     | V    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing beyond the supply rails must be current-limited to 10 mA or less.

## THERMAL INFORMATION

|                         |                                              | AFE4490   |       |

|-------------------------|----------------------------------------------|-----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                | RHA (QFN) | UNITS |

|                         |                                              | 40 PINS   |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 35        |       |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 31        |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 26        | °C/W  |

| ΨJT                     | Junction-to-top characterization parameter   | 0.1       | C/VV  |

| Ψ <sub>JB</sub>         | Junction-to-board characterization parameter | N/A       |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | N/A       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

SBAS602B - DECEMBER 2012 - REVISED FEBRUARY 2013

# RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range, unless otherwise noted.

|             | PARAMETER                   | VALUE                      | UNIT                                                                                          |    |

|-------------|-----------------------------|----------------------------|-----------------------------------------------------------------------------------------------|----|

| SUPPLIES    |                             |                            |                                                                                               |    |

| RX_ANA_SUP  | AFE analog supply           |                            | 2.0 to 3.6                                                                                    | V  |

| RX_DIG_SUP  | AFE digital supply          |                            | 2.0 to 3.6                                                                                    | V  |

| TX_CTRL_SUP | Transmit controller supply  |                            | 3.0 to 5.25                                                                                   | V  |

|             |                             | H-bridge configuration     | [3.0 or $(1.4 + V_{LED} + V_{CABLE})^{(1)(2)}$ ,<br>whichever is greater] to 5.25             | V  |

| LED_DRV_SUP | Transmit LED driver supply  | Common anode configuration | [3.0 or (1.3 + $V_{LED}$ + $V_{CABLE}$ ) <sup>(1)(2)</sup> ,<br>whichever is greater] to 5.25 | V  |

|             | Difference between LED_DRV_ | SUP and TX_CTRL_SUP        | -0.3 to +0.3                                                                                  | V  |

| TEMPERATURE |                             |                            |                                                                                               |    |

|             | Specified temperature range |                            | -40 to +85                                                                                    | °C |

|             | Storage temperature range   |                            | -60 to +150                                                                                   | °C |

(1) V<sub>LED</sub> refers to the voltage drop across the external LED connected between the TXP and TXM pins (in H-bridge mode) and from the TXP and TXM pins to LED\_DRV\_SUP (in the common anode configuration).

(2) V<sub>CABLE</sub> refers to voltage drop across any cable, connector, or any other component in series with the LED.

www.ti.com

STRUMENTS

XAS

## ELECTRICAL CHARACTERISTICS

Minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +85°C. Typical specifications are at +25°C. All specifications are at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 5 V, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

| )            | μA                                               |

|--------------|--------------------------------------------------|

| )            | μA                                               |

| )            | μA                                               |

| 5            | μA                                               |

| 2            | μA                                               |

|              | μA                                               |

| 5            | μA                                               |

| 5000         | SPS                                              |

| 25%          |                                                  |

| )            | μA                                               |

| 5            | μA                                               |

| 5            | dB                                               |

| )            | dB                                               |

| )            | dB                                               |

| 6            | pA <sub>RMS</sub>                                |

| 3            | pA <sub>RMS</sub>                                |

| 3            | Bits                                             |

| 5            | Bits                                             |

|              |                                                  |

| 1            | рА <sub>RMS</sub>                                |

| 5            | рА <sub>RMS</sub>                                |

|              |                                                  |

| nnel section | V/µA                                             |

| þ            |                                                  |

|              | Ω                                                |

| 2            |                                                  |

| and 250      | pF                                               |

| 2            |                                                  |

| 1            | V                                                |

| )            | V                                                |

| 1000         | pF                                               |

| )            | V                                                |

|              | NK, 250K,<br>M<br>and 250<br>5<br>1<br>9<br>1000 |

(1) Noise-free bits  $(N_{FB})$  are defined as:

$$N_{FB} = \log 2 \left[ \frac{I_{PD}}{6.6 \times I_{NOISE}} \right]$$

Where:

$I_{\text{PD}}$  is the photodiode current, and  $I_{\text{NOISE}}$  is the input-referred RMS noise current.

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

Minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +85°C. Typical specifications are at +25°C. All specifications are at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 5 V, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

|       | PARAMETER                                   | TEST CONDITIONS                                                                                                                              | MIN TYP MA                                                                             | X UNIT           |

|-------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|

| AMBIE | NT CANCELLATION STAGE                       |                                                                                                                                              |                                                                                        |                  |

| G     | Gain                                        |                                                                                                                                              | 1, 1.5, 2, 3, and 4                                                                    | V/V              |

|       | Current DAC range                           |                                                                                                                                              | 0                                                                                      | 10 µA            |

|       | Current DAC step size                       |                                                                                                                                              | 1                                                                                      | μA               |

| LOW-F | PASS FILTER                                 | · ·                                                                                                                                          |                                                                                        |                  |

|       | Low-pass corner frequency                   | 3-dB attenuation                                                                                                                             | 0.5 and 1                                                                              | kHz              |

|       |                                             | Duty cycle = 25%                                                                                                                             | 0.004                                                                                  | dB               |

|       | Pass-band attenuation, 2 Hz to 10 Hz        | Duty cycle = 10%                                                                                                                             | 0.041                                                                                  | dB               |

| ANALO | DG-TO-DIGITAL CONVERTER                     |                                                                                                                                              | +                                                                                      |                  |

|       | Resolution                                  |                                                                                                                                              |                                                                                        | 22 Bits          |

|       | Sample rate                                 | See the ADC Operation and Averaging<br>Module section                                                                                        | 4 × PRF                                                                                | SPS              |

|       | ADC full-scale voltage                      |                                                                                                                                              | ±1.2                                                                                   | V                |

|       | ADC conversion time                         | See the ADC Operation and Averaging<br>Module section                                                                                        | 50 PRF                                                                                 | /4 µs            |

|       | ADC reset time                              |                                                                                                                                              | 2                                                                                      | t <sub>CLK</sub> |

| TRANS | SMITTER                                     |                                                                                                                                              |                                                                                        |                  |

|       | Output current range                        |                                                                                                                                              | 0, 50, 75, 100, 150, and 200<br>(see the LEDCNTRL: LED Contro<br>Register for details) | l mA             |

|       | LED current DAC error                       |                                                                                                                                              | ±5%                                                                                    |                  |

|       | Output current resolution                   |                                                                                                                                              | 8                                                                                      | Bits             |

|       | Transmitter noise dynamic range,            | At 25-mA output current                                                                                                                      | 110                                                                                    |                  |

|       | over 0.1-Hz to 5-Hz bandwidth               | At 100-mA output current                                                                                                                     | 110                                                                                    |                  |

|       | Minimum sample time of LED1 and LED2 pulses |                                                                                                                                              | 50                                                                                     | μs               |

|       |                                             | LED_ON = 0                                                                                                                                   | 1                                                                                      | μA               |

|       | LED current DAC leakage current             | LED_ON = 1                                                                                                                                   | 50                                                                                     | μA               |

|       | LED current DAC linearity                   | Percent of full-scale current                                                                                                                | 0.5%                                                                                   |                  |

|       | Output current settling time                | From zero current to 150 mA                                                                                                                  | 7                                                                                      | μs               |

|       | (with resistive load)                       | From 150 mA to zero current                                                                                                                  | 7                                                                                      | μs               |

| DIAGN | OSTICS                                      |                                                                                                                                              |                                                                                        |                  |

|       |                                             | EN_SLOW_DIAG = 0<br>Start of diagnostics after the DIAG_EN<br>register bit is set.<br>End of diagnostic indicated by DIAG_END<br>going high. | 8                                                                                      | ms               |

|       | Duration of diagnostics state machine       | EN_SLOW_DIAG = 1<br>Start of diagnostics after the DIAG_EN<br>register bit is set.<br>End of diagnostic indicated by DIAG_END<br>going high. | 16                                                                                     | ms               |

|       | Open fault resistance                       |                                                                                                                                              | > 100                                                                                  | kΩ               |

|       | Short fault resistance                      |                                                                                                                                              | < 10                                                                                   | kΩ               |

EXAS

## **ELECTRICAL CHARACTERISTICS (continued)**

Minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +85°C. Typical specifications are at +25°C. All specifications are at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 5 V, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

|                      | PARAMETER                                            | TEST CONDITIONS                                                   | MIN TYP MAX       | UNIT             |

|----------------------|------------------------------------------------------|-------------------------------------------------------------------|-------------------|------------------|

| INTERNAL             | OSCILLATOR                                           |                                                                   |                   |                  |

| f <sub>CLKOUT</sub>  | CLKOUT frequency                                     | With an 8-MHz crystal connected to the XIN and XOUT pins          | 4                 | MHz              |

| DC <sub>CLKOUT</sub> | CLKOUT duty cycle                                    |                                                                   | 50%               |                  |

|                      | Crystal oscillator start-up time                     | With an 8-MHz crystal connected to the XIN and XOUT pins          | 200               | μs               |

| EXTERNAL             | L CLOCK                                              |                                                                   |                   |                  |

|                      | Maximum allowable external clock jitter              |                                                                   | 50                | ps               |

| TIMING               |                                                      |                                                                   |                   |                  |

|                      | Wake-up time from complete power-down                |                                                                   | 1000              | ms               |

| t <sub>RESET</sub>   | Active low RESET pulse duration                      |                                                                   | 1                 | μs               |

| t <sub>DIAGEND</sub> | DIAG_END pulse duration at diagnostics<br>completion |                                                                   | 4                 | CLKOUT<br>cycles |

| t <sub>ADCRDY</sub>  | ADC_RDY pulse duration                               |                                                                   | 1                 | CLKOUT<br>cycles |

| DIGITAL S            | IGNAL CHARACTERISTICS                                |                                                                   |                   |                  |

| V <sub>IH</sub>      | Logic high input voltage                             | AFE_PDN, SPI CLK, SPI SIMO, SPI STE,<br>RESET                     | 0.75 × RX_DIG_SUP | V                |

| V <sub>IL</sub>      | Logic low input voltage                              | AFE_PDN, SPI CLK, SPI SIMO, SPI STE,<br>RESET                     | 0.25 × RX_DIG_SUP | V                |

| I <sub>IN</sub>      | Logic input current                                  | Digital inputs at $V_{IH}$ or $V_{IL}$                            | 0.1               | μA               |

| V <sub>OH</sub>      | Logic high output voltage                            | DIAG_END, LED_ALM, PD_ALM, SPI SOMI, ADC_RDY, CLKOUT              | RX_DIG_SUP - 0.1  | V                |

| V <sub>OL</sub>      | Logic low output voltage                             | DIAG_END, LED_ALM, PD_ALM, SPI SOMI, ADC_RDY, CLKOUT              | 0.1               | V                |

| SUPPLY C             | URRENT                                               |                                                                   |                   |                  |

|                      |                                                      | RX_ANA_SUP = 3.0 V, with 8-MHz clock running, Rx stage 2 disabled | 0.6               | mA               |

|                      | Receiver analog supply current                       | RX_ANA_SUP = 3.0 V, with 8-MHz clock running, Rx stage 2 enabled  | 0.7               | mA               |

|                      | Receiver digital supply current                      | RX_DIG_SUP = 3.0 V                                                | 0.27              | mA               |

| LED_DRV<br>_SUP      | LED driver supply current                            | With zero LED current setting                                     | 55                | μA               |

| TX_CTRL<br>_SUP      | Transmitter control supply current                   |                                                                   | 15                | μA               |

|                      | Complete power-down                                  | Receiver current only<br>(RX_ANA_SUP + RX_DIG_SUP)                | 5                 | μA               |

|                      | (using the AFE_PDN pin)                              | Transmitter current only<br>(LED_DRV_SUP + TX_CTRL_SUP)           | 2                 | μA               |

|                      | Power-down Rx alone                                  | Receiver current only<br>(RX_ANA_SUP + RX_DIG_SUP)                | 220               | μA               |

|                      | Power-down Tx alone                                  | Transmitter current only<br>(LED_DRV_SUP + TX_CTRL_SUP)           | 2                 | μA               |

|                      |                                                      |                                                                   |                   |                  |

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

Minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +85°C. Typical specifications are at +25°C. All specifications are at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 5 V, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

| PARAMETER         |                                              |             | TEST CONDITIONS                                             | MIN TYP MAX | UNIT |

|-------------------|----------------------------------------------|-------------|-------------------------------------------------------------|-------------|------|

| POWER             | DISSIPATION                                  |             |                                                             |             |      |

| <b>D</b>          | Quiescent power dissipation                  |             | Normal operation (excluding LEDs)                           | 1.54        | mW   |

| P <sub>D(q)</sub> |                                              |             | Power-down                                                  | 0.1         | μW   |

|                   |                                              | LED_DRV_SUP | LED_DRV_SUP current value.<br>Does not include LED current. | 1           | μA   |

|                   | Power-down with the                          | TX_CTRL_SUP |                                                             | 1           | μA   |

|                   | AFE_PDN pin                                  | RX_ANA_SUP  |                                                             | 5           | μA   |

|                   |                                              | RX_DIG_SUP  |                                                             | 0.1         | μA   |

|                   |                                              | LED_DRV_SUP | LED_DRV_SUP current value.<br>Does not include LED current. | 1           | μA   |

|                   | Power-down with the                          | TX_CTRL_SUP |                                                             | 1           | μA   |

|                   | PDNAFE register bit                          | RX_ANA_SUP  |                                                             | 15          | μA   |

|                   |                                              | RX_DIG_SUP  |                                                             | 20          | μA   |

|                   |                                              | LED_DRV_SUP | LED_DRV_SUP current value.<br>Does not include LED current. | 50          | μA   |

|                   | Power-down Rx                                | TX_CTRL_SUP |                                                             | 15          | μA   |

|                   |                                              | RX_ANA_SUP  |                                                             | 220         | μA   |

|                   |                                              | RX_DIG_SUP  |                                                             | 220         | μA   |

|                   |                                              | LED_DRV_SUP | LED_DRV_SUP current value.<br>Does not include LED current. | 2           | μA   |

|                   | Power-down Tx                                | TX_CTRL_SUP |                                                             | 2           | μA   |

|                   |                                              | RX_ANA_SUP  |                                                             | 600         | μA   |

|                   |                                              | RX_DIG_SUP  |                                                             | 230         | μA   |

|                   |                                              | LED_DRV_SUP | LED_DRV_SUP current value.<br>Does not include LED current. | 50          | μA   |

|                   | After reset, with 8-MHz                      | TX_CTRL_SUP |                                                             | 15          | μA   |

|                   | clock running                                | RX_ANA_SUP  |                                                             | 600         | μA   |

|                   |                                              | RX_DIG_SUP  |                                                             | 230         | μA   |

|                   |                                              | LED_DRV_SUP | LED_DRV_SUP current value.<br>Does not include LED current. | 0.28        | μA   |

|                   | With stage 2 mode<br>enabled and 8-MHz clock | TX_CTRL_SUP |                                                             | 0.1         | μA   |

|                   | running                                      | RX_ANA_SUP  |                                                             | 700         | μA   |

|                   |                                              | RX_DIG_SUP  |                                                             | 0.8         | μA   |

TEXAS INSTRUMENTS

www.ti.com

## PARAMETRIC MEASUREMENT INFORMATION

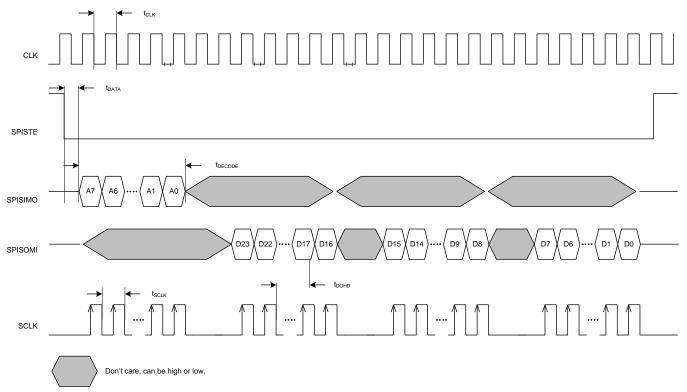

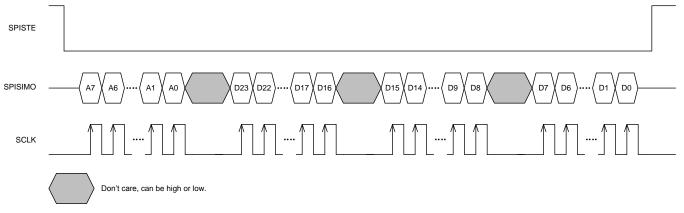

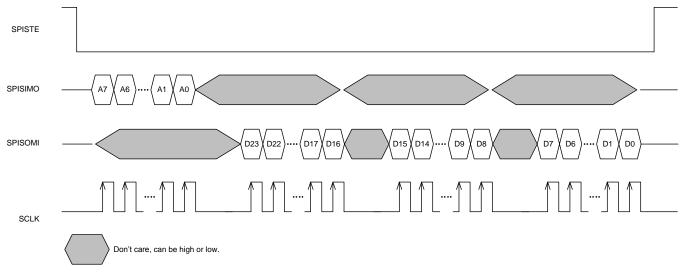

## SERIAL INTERFACE TIMING

(1) The SPI\_READ register bit must be enabled before attempting a serial readout from the AFE.

- (2) Specify the register address whose contents must be read back on A[7:0].

- (3) The AFE outputs the contents of the specified register on the SOMI pin.

# Figure 1. Serial Interface Timing Diagram<sup>(1)(2)(3)</sup>

|                       | PARAMETER                                                      | 2.0 V ≤ RX_             | UNIT |     |      |

|-----------------------|----------------------------------------------------------------|-------------------------|------|-----|------|

|                       | PARAMETER                                                      | MIN                     | TYP  | MAX | UNIT |

| f <sub>SPICLK</sub>   | SPI CLK frequency                                              |                         |      | 8   | MHz  |

| t <sub>SPI_SU</sub>   | SPISIMO input data setup time with respect to SCLK rising edge | 62.5                    |      |     | ns   |

| t <sub>SPI_HO</sub>   | SPISIMO input data hold time with respect to SCLK rising edge  | 62.5                    |      |     | ns   |

| t <sub>SOMI_VAL</sub> | SPISOMI output data setup time                                 | t <sub>SPICLK</sub> / 4 |      |     | ns   |

| t <sub>SOMI_HO</sub>  | SPISOMI output data hold time                                  | t <sub>SPICLK</sub> / 2 |      |     | ns   |

| t <sub>RISE</sub>     | Rise time from 20% to 80%                                      |                         | 5    |     | ns   |

| t <sub>FALL</sub>     | Fall time from 80% to 20%                                      |                         | 5    |     | ns   |

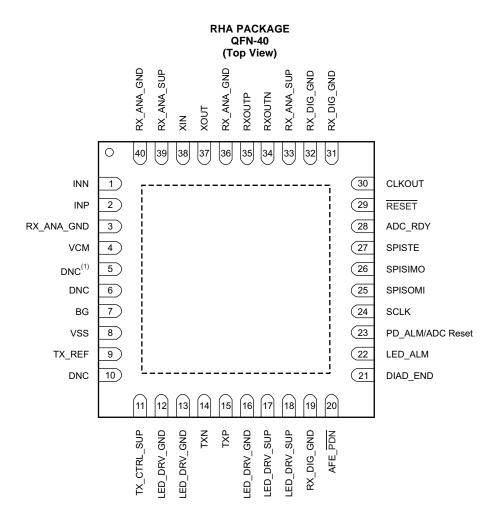

### **PIN CONFIGURATION**

(4) DNC = Do not connect.

### **PIN DESCRIPTIONS**

| NAME               | NO.        | FUNCTION  | DESCRIPTION                                                                                                                                         |

|--------------------|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC_RDY            | 28         | Digital   | Output signal that indicates ADC conversion completion.<br>Can be connected to the interrupt input pin of an external microcontroller.              |

| AFE_PDN            | 20         | Digital   | AFE-only power-down input; active low.<br>Can be connected to the port pin of an external microcontroller.                                          |

| BG                 | 7          | Reference | Decoupling capacitor for internal band-gap voltage to ground.<br>(2.2- $\mu$ F decoupling capacitor to ground, expected voltage = 1.0 V.)           |

| CLKOUT             | 30         | Digital   | Buffered 4-MHz output clock output.<br>Can be connected to the clock input pin of an external microcontroller.                                      |

| DIAG_END           | 21         | Digital   | Output signal that indicates completion of diagnostics.<br>Can be connected to the port pin of an external microcontroller.                         |

| DNC <sup>(1)</sup> | 5, 6, 10   | _         | Do not connect these pins. Leave as open-circuit.                                                                                                   |

| INN                | 1          | Analog    | Receiver input pin. Connect to photodiode anode.                                                                                                    |

| INP                | 2          | Analog    | Receiver input pin. Connect to photodiode cathode.                                                                                                  |

| LED_DRV_GND        | 12, 13, 16 | Supply    | LED driver ground pin, H-bridge. Connect to common board ground.                                                                                    |

| LED_DRV_SUP        | 17, 18     | Supply    | LED driver supply pin, H-bridge. Connect to an external power supply capable of supplying the large LED current, which is drawn by this supply pin. |

| LED_ALM            | 22         | Digital   | Output signal that indicates an LED cable fault.<br>Can be connected to the port pin of an external microcontroller.                                |

(1) Leave pins as open circuit. Do not connect.

Copyright © 2012–2013, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

www.ti.com

NSTRUMENTS

Texas

# **PIN DESCRIPTIONS (continued)**

| NAME             | NO.       | FUNCTION  | DESCRIPTION                                                                                                                                                                                                                                      |

|------------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD_ALM/ADC Reset | 23        | Digital   | Output signal that indicates a PD sensor or cable fault.<br>Can be connected to the port pin of an external microcontroller.<br>In ADC bypass mode, the PD_ALM pin can be used to bring out the ADC reset signal.                                |

| RESET            | 29        | Digital   | AFE-only reset input, active low.<br>Can be connected to the port pin of an external microcontroller.                                                                                                                                            |

| RX_ANA_GND       | 3, 36, 40 | Supply    | Rx analog ground pin. Connect to common board ground.                                                                                                                                                                                            |

| RX_ANA_SUP       | 33, 39    | Supply    | Rx analog supply pin (2.0 V to 3.6 V); 0.1-µF decoupling capacitor to ground                                                                                                                                                                     |

| RX_DIG_GND       | 19, 32    | Supply    | Rx digital ground pin. Connect to common board ground.                                                                                                                                                                                           |

| RX_DIG_SUP       | 31        | Supply    | Rx digital supply pin (2.0 V to 3.6 V); 0.1-µF decoupling capacitor to ground                                                                                                                                                                    |

| RXOUTN           | 34        | Analog    | External ADC negative input when in ADC bypass mode                                                                                                                                                                                              |

| RXOUTP           | 35        | Analog    | External ADC positive input when in ADC bypass mode                                                                                                                                                                                              |

| SCLK             | 24        | SPI       | SPI clock pin                                                                                                                                                                                                                                    |

| SPISIMO          | 26        | SPI       | SPI serial in master out                                                                                                                                                                                                                         |

| SPISOMI          | 25        | SPI       | SPI serial out master in                                                                                                                                                                                                                         |

| SPISTE           | 27        | SPI       | SPI serial interface enable                                                                                                                                                                                                                      |

| TX_CTRL_SUP      | 11        | Supply    | Transmit control supply pin, 5 V (0.1-µF decoupling capacitor to ground)                                                                                                                                                                         |

| TX_REF           | 9         | Reference | Tx reference voltage                                                                                                                                                                                                                             |

| TXN              | 14        | Analog    | LED driver out B, H-bridge output. Connect to LED.                                                                                                                                                                                               |

| TXP              | 15        | Analog    | LED driver out B, H-bridge output. Connect to LED.                                                                                                                                                                                               |

| VCM              | 4         | Reference | Input common-mode voltage output.<br>Connect a series resistor (1 k $\Omega$ ) and a decoupling capacitor (10 nF) to ground.<br>The voltage across the capacitor can be used to shield (guard) the INP, INM traces.<br>Expected voltage = 0.9 V. |

| VSS              | 8         | Supply    | Substrate ground. Connect to common board ground.                                                                                                                                                                                                |

| XOUT             | 37        | Digital   | Crystal oscillator pins.<br>Connect an external 8-MHz crystal between these pins with the correct load capacitor<br>(as specified by vendor) to ground.                                                                                          |

| XIN              | 38        | Digital   | Crystal oscillator pins.<br>Connect an external 8-MHz crystal between these pins with the correct load capacitor<br>(as specified by vendor) to ground.                                                                                          |

TEXAS INSTRUMENTS

SBAS602B-DECEMBER 2012-REVISED FEBRUARY 2013

www.ti.com

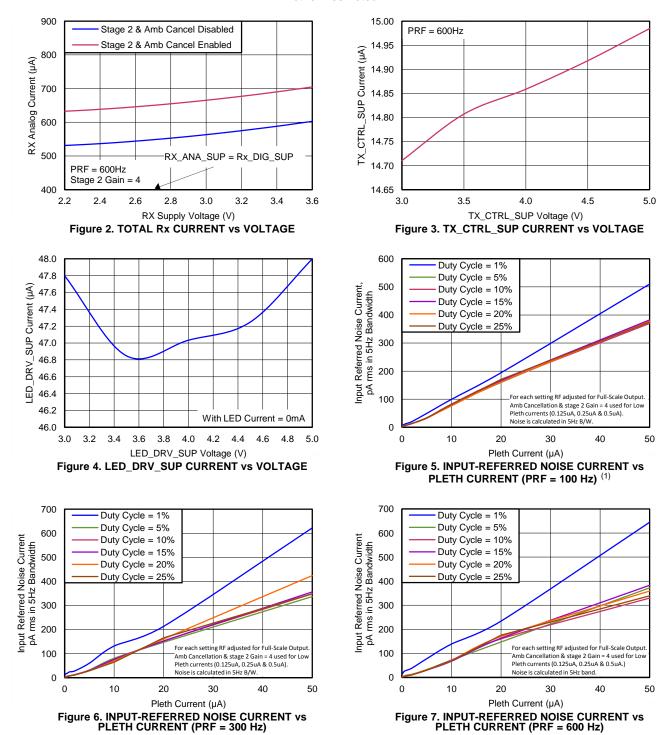

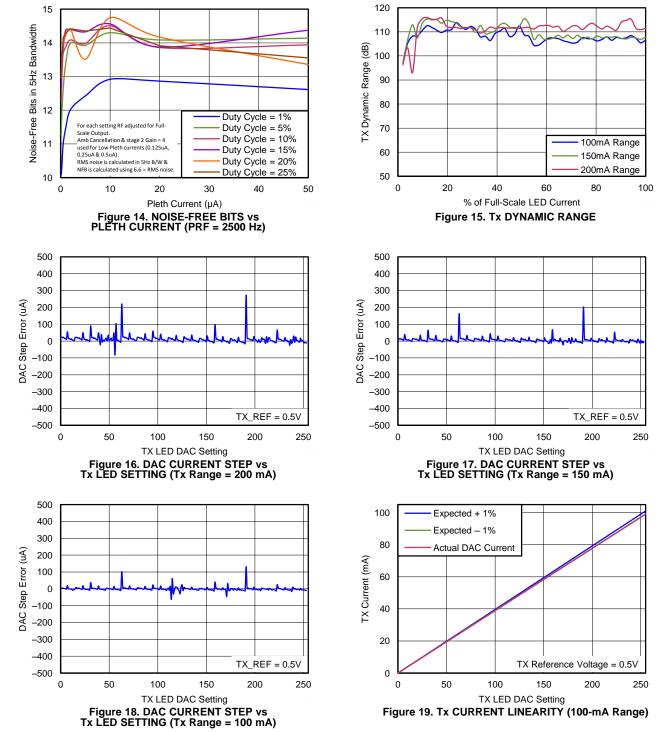

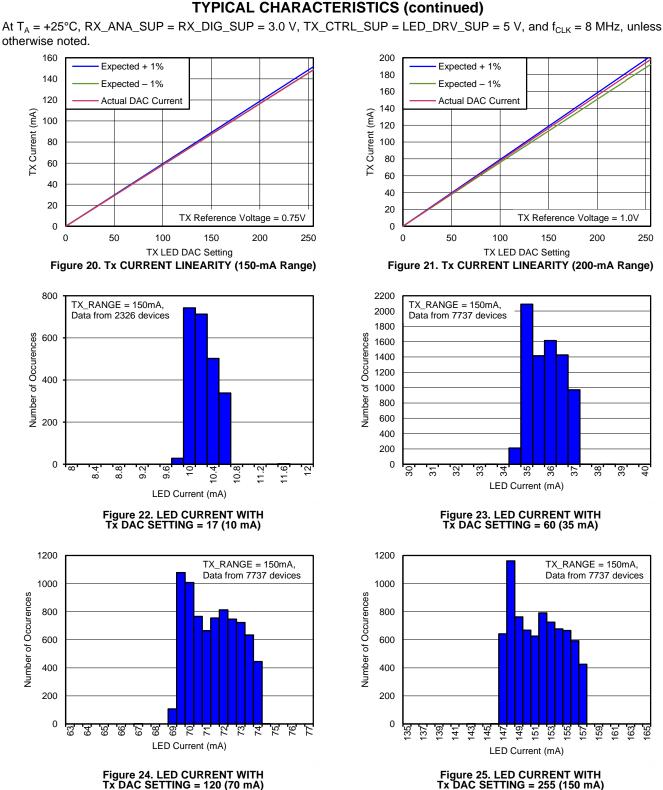

### **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ , RX\_ANA\_SUP = RX\_DIG\_SUP = 3.0 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 5 V, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

www.ti.com

#### 800 1400 or each setting RF adjusted for Full-Scale Outp Amb Cancellation & stage 2 Gain = 4 used for .ow Pleth currents (0.125uA, 0.25uA & 0.5uA). Noise is calculated in 5Hz band. Duty Cycle = 1% Duty Cycle = 1% Duty Cycle = 5% Duty Cycle = 5% 700 1200 Duty Cycle = 10% Input Referred Noise Current. pA rms in 5Hz Bandwidth Duty Cycle = 10% Input Referred Noise Current pA rms in 5Hz Bandwidth 600 Duty Cycle = 15% Duty Cycle = 15% 1000 Duty Cycle = 20% Duty Cycle = 20% 500 Duty Cycle = 25% Duty Cycle = 25% 800 400 600 300 400 200 For each RF adjusted for Full-Scale Output. Amb Cancellation & stage 2 Gain = 4 used for Lu Pleth currents (0.125uA, 0.25uA & 0.5uA). 200 100 Noise is calculated in 5Hz band. 0 0 0 10 20 30 40 50 0 10 20 30 40 50 Pleth Current ( µA) Pleth Current ( µA) Figure 8. INPUT-REFERRED NOISE CURRENT vs PLETH CURRENT (PRF = 1200 Hz) Figure 9. INPUT-REFERRED NOISE CURRENT vs PLETH CURRENT (PRF = 2500 Hz) 16 16 or each setting RF adjusted for Full-Scale Output. mb Cancellation & stage 2 Gain = 4 used for Low Pleth currents (0.125uA, 0.25uA & 0.5uA). MS noise is calculated in 5Hz B/W & NFB is calculated using 6.6 × RMS noise. or each setting RF adjusted for Full-Scale Output. mb Cancellation & stage 2 Gain = 4 used for Low pleth currents (0.125uA, 0.25uA & 0.5uA.) MS noise is calculated in 5Hz B/W & NFB is calculated using 6.6 × RMS noise. Noise-Free Bits in 5Hz Bandwidth Noise-Free Bits in 5Hz Bandwidth 15 15 14 14 13 13 Duty Cycle = 1% Duty Cycle = 1% Duty Cycle = 5% Duty Cycle = 5% 12 12 Duty Cycle = 10% Duty Cycle = 10% Duty Cycle = 15% Duty Cycle = 15% 11 11 Duty Cycle = 20% Duty Cycle = 20% Duty Cycle = 25% Duty Cycle = 25% 10 10 0 10 20 30 40 50 0 10 20 30 40 50 Pleth Current (µA) Pleth Current (µA) Figure 10. NOISE-FREE BITS vs PLETH CURRENT (PRF = 100 Hz) Figure 11. NOISE-FREE BITS vs PLETH CURRENT (PRF = 300 Hz) 16 16 or each setting RF adjusted for Full-Scale Output. or each setting RF adjusted for Full-Scale Output. mb Cancellation & stage 2 Gain = 4 used for Low Pleth currents (0.125uA, 0.25uA & 0.5uA). nb Cancellation & stage 2 Gain = 4 used for Low Pleth currents (0.125uA, 0.25uA & 0.5uA). //S noise is calculated in 5Hz B/W & NFB is calculated using 6.6 × RMS noise. MS noise is calculated in 5Hz B/W & NFB is calculated using 6.6 × RMS noise Noise-Free Bits in 5Hz Bandwidth Noise-Free Bits in 5Hz Bandwidth 15 15 14 14 13 13 Duty Cycle = 1% Duty Cycle = 1% 12 Duty Cycle = 5% 12 Duty Cycle = 5% Duty Cycle = 10% Duty Cycle = 10% Duty Cycle = 15% Duty Cycle = 15% 11 11 Duty Cycle = 20% Duty Cycle = 20% Duty Cycle = 25% Duty Cycle = 25% 10 10 0 10 20 30 40 50 0 10 20 30 40 50 Pleth Current (µA) Pleth Current (µA) Figure 13. NOISE-FREE BITS vs PLETH CURRENT (PRF = 1200 Hz) Figure 12. NOISE-FREE BITS vs PLETH CURRENT (PRF = 600 Hz) (2)

**TYPICAL CHARACTERISTICS (continued)**

At T<sub>A</sub> = +25°C, RX\_ANA\_SUP = RX\_DIG\_SUP = 3.0 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 5 V, and f<sub>CLK</sub> = 8 MHz, unless otherwise noted.

TEXAS INSTRUMENTS

SBAS602B-DECEMBER 2012-REVISED FEBRUARY 2013

#### www.ti.com

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C, RX\_ANA\_SUP = RX\_DIG\_SUP = 3.0 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 5 V, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

**Texas NSTRUMENTS**

www.ti.com

Tx DAC SETTING = 255 (150 mA)

**AFE4490**

#### www.ti.com

### **OVERVIEW**

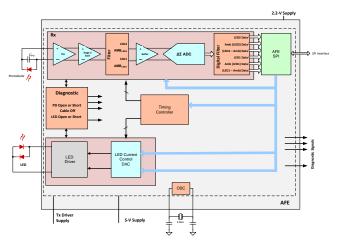

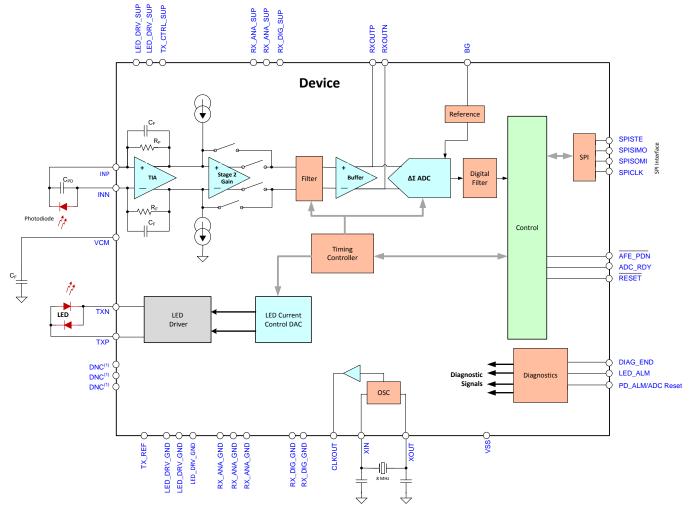

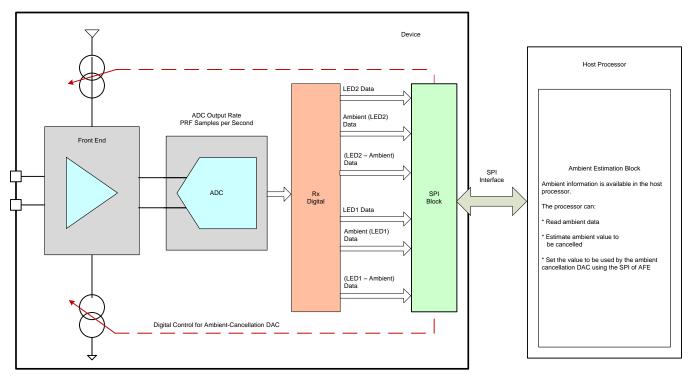

The AFE4490 is a complete analog front-end (AFE) solution targeted for pulse-oximeter applications. The device consists of a low-noise receiver channel, an LED transmit section, and diagnostics for sensor and LED fault detection. To ease clocking requirements and provide the low-jitter clock to the AFE, an oscillator is also integrated that functions from an external crystal. The device communicates to an external microcontroller or host processor using an SPI interface. Figure 26 shows a detailed block diagram for the AFE4490. The blocks are described in more detail in the following sections.

Figure 26. Detailed Block Diagram

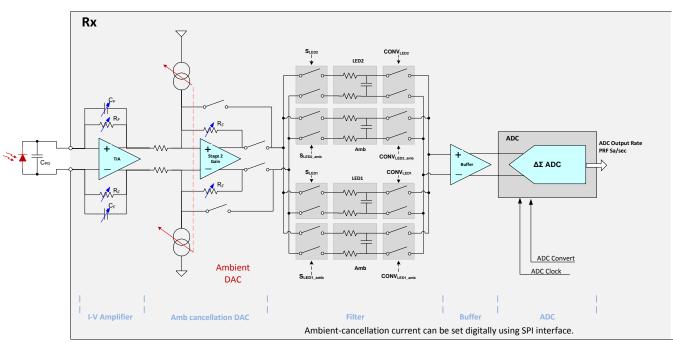

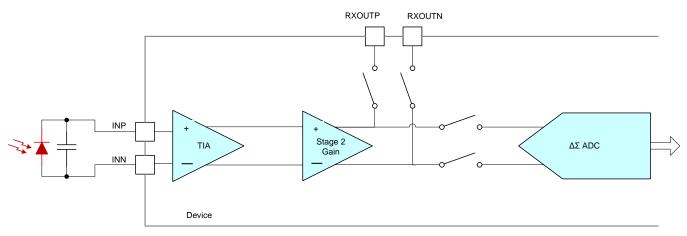

# **RECEIVER CHANNEL**

This section describes the receiver channel functionality.

# **Receiver Front-End**

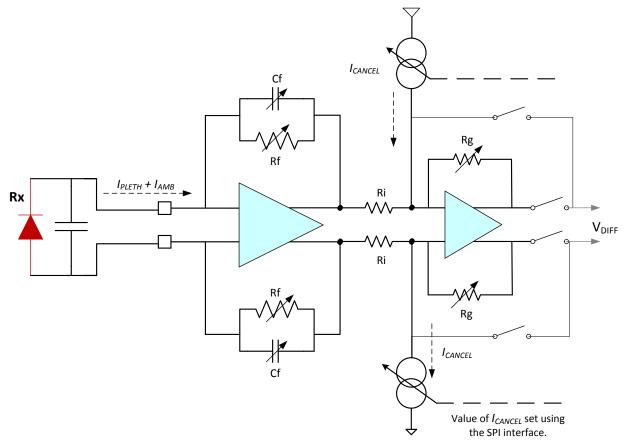

The receiver consists of a differential current-to-voltage (I-V) transimpedance amplifier that converts the input photodiode current into an appropriate voltage, as shown in Figure 27. The feedback resistor of the amplifier (R<sub>F</sub>) is programmable to support a wide range of photodiode currents. Available R<sub>F</sub> values include: 1 M $\Omega$ , 500 k $\Omega$ , 250 k $\Omega$ , 100 k $\Omega$ , 50 k $\Omega$ , 25 k $\Omega$ , and 10 k $\Omega$ .

Figure 27. Receiver Front-End

The R<sub>F</sub> amplifier and the feedback capacitor (C<sub>F</sub>) form a low-pass filter for the input signal current. Always ensure that the low-pass filter has sufficiently high bandwidth (as shown by Equation 1) because the input current consists of pulses. For this reason, the feedback capacitor is also programmable. Available C<sub>F</sub> values include: 5 pF, 10 pF, 25 pF, 50 pF, 100 pF, and 250 pF. Any combination of these capacitors can also be used.

$$R_F \times C_F \le \frac{Rx \text{ Sample Time}}{10}$$

(1)

The output voltage of the I-V amplifier includes the pleth component (the desired signal) and a component resulting from the ambient light leakage. The I-V amplifier is followed by the second stage, which consists of a current digital-to-analog converter (DAC) that sources the cancellation current and an amplifier that gains up the pleth component alone. The amplifier has five programmable gain settings: 1, 1.5, 2, 3, and 4. The gained-up pleth signal is then low-pass filtered (500-Hz bandwidth) and buffered before driving a 22-bit ADC. The current DAC has a cancellation current range of 10  $\mu$ A with 10 steps (1  $\mu$ A each). The DAC value can be digitally specified with the SPI interface.

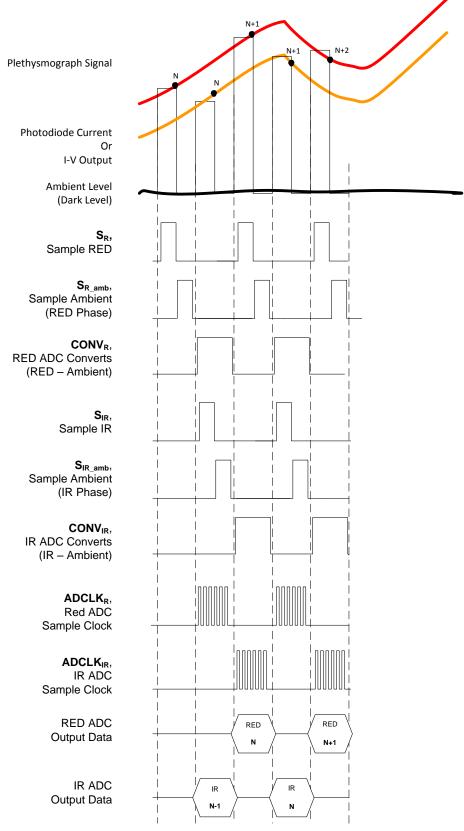

The output of the ambient cancellation amplifier is separated into LED2 and LED1 channels. When LED2 is on, the amplifier output is filtered and sampled on capacitor  $C_R$ . Similarly, the LED1 signal is sampled on the  $C_{LED1}$  capacitor when LED1 is ON. In between the LED2 and LED1 pulses, the idle amplifier output is sampled to estimate the ambient signal on capacitors  $C_{LED2\_amb}$  and  $C_{LED1\_amb}$ .

The sampling duration is termed the *Rx* sample time and is programmable for each signal, independently. Sampling can start after the I-V amplifier output is stable (to account for LED and cable settling times). The Rx sample time is used for all dynamic range calculations; the minimum time supported is 50  $\mu$ s.

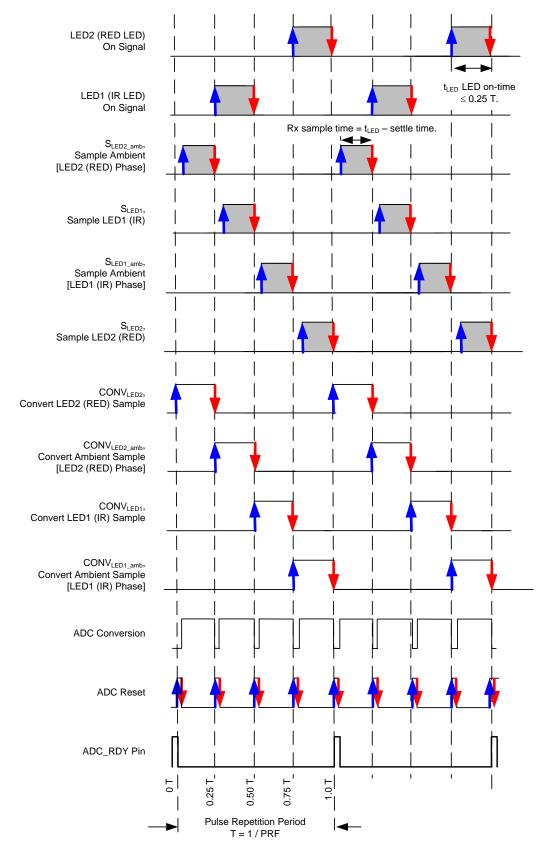

#### SBAS602B – DECEMBER 2012 – REVISED FEBRUARY 2013

A single, 22-bit ADC converts the sampled LED2, LED1, and ambient signals sequentially. Each conversion takes a maximum of 25% of the pulse repetition period (PRP) and provides a single digital code at the ADC output. As discussed in the *Receiver Timing* section, the conversions are staggered so that the LED2 conversion starts after the end of the LED2 sample phase, and so on. This configuration also means that the Rx sample time for each signal is no greater than 25% of the pulse repetition period.

Note that four data streams are available at the ADC output (LED2, LED1, ambient LED2, and ambient LED1) at the same rate as the pulse repetition frequency. The ADC is followed by a digital ambient subtraction block that additionally outputs the (LED2 – ambient LED2) and (LED1 – ambient LED1) data values.

### Ambient Cancellation Scheme

The receiver provides digital samples corresponding to ambient duration. The host processor (external to the AFE) can use these ambient values to estimate the amount of ambient light leakage. The processor must then set the value of the ambient cancellation DAC using the SPI, as shown in Figure 28.

Figure 28. Ambient Cancellation Loop (Closed by the Host Processor)

TEXAS INSTRUMENTS

SBAS602B – DECEMBER 2012 – REVISED FEBRUARY 2013

www.ti.com

Using the set value, the ambient cancellation stage subtracts the ambient component and gains up only the pleth component of the received signal, as shown in Figure 29.

The amplifier gain is programmable to 1, 1.5, 2, 3, and 4.

Figure 29. Front-End (I-V Amplifier and Cancellation Stage)

The differential output of the second stage is  $V_{DIFF}$ , as given by Equation 2:

$$V_{\text{DIFF}} = 2 \times \left( I_{\text{PLETH}} \times \frac{R_{\text{F}}}{R_{\text{I}}} + I_{\text{AMB}} \times \frac{R_{\text{F}}}{R_{\text{I}}} - I_{\text{CANCEL}} \right) \times R_{\text{G}}$$

Where:

$R_{l} = 100 \text{ k}\Omega,$

I<sub>PLETH</sub> = photodiode current pleth component,

$I_{AMB}$  = photodiode current ambient component, and

$I_{CANCEL}$  = the cancellation current DAC value (as estimated by the host processor).

(2)

AFE4490

#### www.ti.com

### **Receiver Control Signals**

**LED2 sample phase (S<sub>LED2</sub>):** When this signal is high, the amplifier output corresponds to the LED2 on-time. The amplifier output is filtered and sampled into capacitor  $C_{LED2}$ . To avoid settling effects resulting from the LED or cable, program  $S_{LED2}$  to start after the LED turns on. This settling delay is programmable.

**Ambient sample phase (S<sub>LED2\_amb</sub>):** When this signal is high, the amplifier output corresponds to the LED2 offtime and can be used to estimate the ambient signal (for the LED2 phase). The amplifier output is filtered and sampled into capacitor  $C_{LED2 amb}$ .

**LED1 sample phase (S**<sub>LED1</sub>): When this signal is high, the amplifier output corresponds to the LED1 on-time. The amplifier output is filtered and sampled into capacitor  $C_{LED1}$ . To avoid settling effects resulting from the LED or cable, program  $S_{LED1}$  to start after the LED turns on. This settling delay is programmable.

**Ambient sample phase (S**<sub>LED1\_amb</sub>): When this signal is high, the amplifier output corresponds to the LED1 offtime and can be used to estimate the ambient signal (for the LED1 phase). The amplifier output is filtered and sampled into capacitor  $C_{LED1 amb}$ .

**LED2 convert phase (CONV**<sub>LED2</sub>): When this signal is high, the voltage sampled on  $C_{LED2}$  is buffered and applied to the ADC for conversion. The conversion time duration is always 25% of the pulse repetition period. At the end of the conversion, the ADC provides a single digital code corresponding to the LED2 sample.

**Ambient convert phases (CONV**<sub>LED2\_amb</sub>, **CONV**<sub>LED1\_amb</sub>): When this signal is high, the voltage sampled on  $C_{LED2\_amb}$  (or  $C_{LED1\_amb}$ ) is buffered and applied to the ADC for conversion. The conversion time duration is always 25% of the pulse repetition period. At the end of the conversion, the ADC provides a single digital code corresponding to the ambient sample.

**LED1 convert phase (CONV**<sub>LED1</sub>): When this signal is high, the voltage sampled on  $C_{LED1}$  is buffered and applied to the ADC for conversion. The conversion time duration is always 25% of the pulse repetition period. At the end of the conversion, the ADC provides a single digital code corresponding to the LED1 sample.

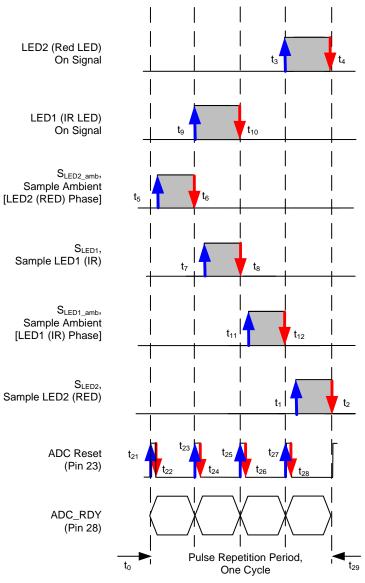

### Receiver Timing

See Figure 30 for a timing diagram detailing the control signals related to the LED on-time, Rx sample time, and the ADC conversion times for each channel.

NOTE: Relationship to the AFE4490EVM is: LED1 = IR and LED2 = RED.

Figure 30. Rx Timing Diagram

#### SBAS602B - DECEMBER 2012 - REVISED FEBRUARY 2013

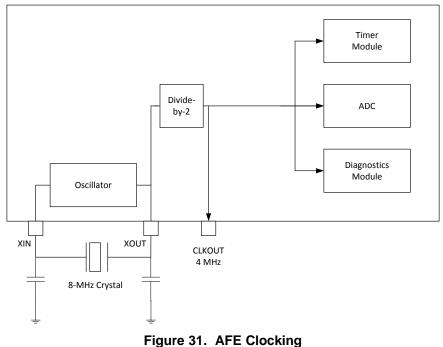

**CLOCKING AND TIMING SIGNAL GENERATION**

The crystal oscillator generates a master clock signal using an external 8-MHz crystal. A divide-by-2 block converts the 8-MHz clock to 4 MHz, which is used by the AFE to operate the timer modules, ADC, and diagnostics. The 4-MHz clock is buffered and output from the AFE in order to clock an external microcontroller. The clocking functionality is shown in Figure 31.

### Figure 51. AFE Clock

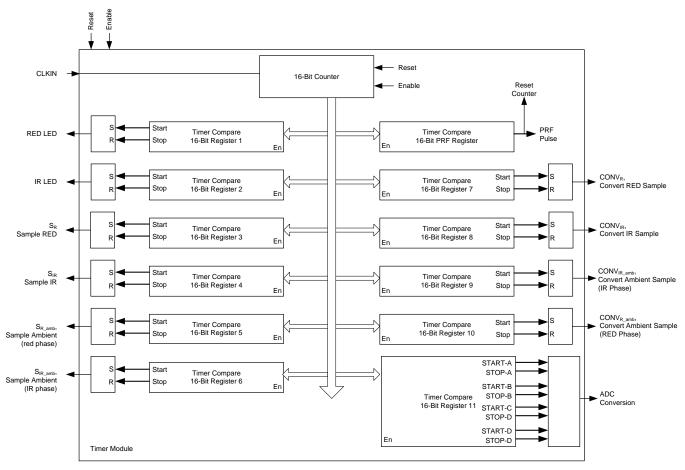

## TIMER MODULE

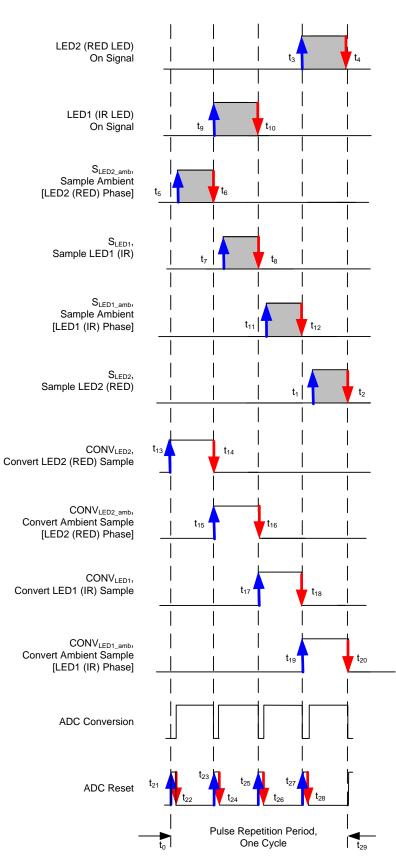

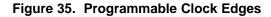

See Figure 32 for a timing diagram detailing the various timing edges that are programmable using the timer module. The rising and falling edge positions of 11 signals can be controlled. The module uses a single 16-bit counter (running off of the 4-MHz clock) to set the time-base.

All timing signals are set with reference to the pulse repetition period (PRP). Therefore, a dedicated compare register compares the 16-bit counter value with the reference value specified in the PRF register. Every time that the 16-bit counter value is equal to the reference value in the PRF register, the counter is reset to '0'.

# AFE4490

SBAS602B-DECEMBER 2012-REVISED FEBRUARY 2013

www.ti.com

NOTE: Programmable edges are shown in blue and red.

### Figure 32. AFE Control Signals

#### SBAS602B – DECEMBER 2012 – REVISED FEBRUARY 2013

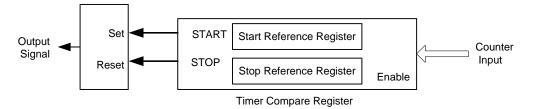

For the 11 signals in Figure 30, the start and stop edge positions are programmable with respect to the PRF period. Each signal uses a separate timer compare module that compares the counter value with preprogrammed reference values for the start and stop edges. All reference values can be set using the SPI interface.

When the counter value equals the start reference value, the output signal is set. When the counter value equals the stop reference value, the output signal is reset. Figure 33 shows a diagram of the timer compare register. With a 4-MHz clock, the edge placement resolution is  $0.25 \,\mu$ s. The ADC conversion signal requires four pulses in each PRF clock period. The 11th timer compare register uses four sets of start and stop registers to control the ADC conversion signal.

Figure 33. Compare Register

The ADC conversion signal requires four pulses in each PRF clock period. Timer compare register 11 uses four sets of start and stop registers to control the ADC conversion signal, as shown in Figure 34.

Figure 34. Timer Module

### Using the Timer Module

The timer module registers can be used to program the start and end instants in units of 4-MHz clock cycles. These timing instants and the corresponding registers are listed in Table 2.

Note that the device does not restrict the values in these registers; thus, the start and end edges can be positioned anywhere within the pulse repetition period. Care must be taken by the user to program suitable values in these registers to avoid overlapping the signals and to make sure none of the edges exceed the value programmed in the PRP register. Writing the same value in the start and end registers results in a pulse duration of one clock cycle. The following steps describe the timer sequencing configuration:

- 1. With respect to the start of the PRP period (indicated by timing instant  $t_0$  in Figure 35), the sequence of conversions must be followed in order: convert LED2  $\rightarrow$  LED2 ambient  $\rightarrow$  LED1  $\rightarrow$  LED1 ambient.

- 2. Also, starting from  $t_0$ , the sequence of sampling instants must be staggered with respect to the respective conversions as follows: sample LED2 ambient  $\rightarrow$  LED1  $\rightarrow$  LED1 ambient  $\rightarrow$  LED2.

- 3. Finally, align the edges for the two LED pulses with the respective sampling instants.

| TIME INSTANT<br>(See Figure 35 and<br>Figure 36) | DESCRIPTION                                | CORRESPONDING REGISTER ADDRESS AND REGISTER BITS             | EXAMPLE<br>(Decimal) |

|--------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|----------------------|

| to                                               | Start of pulse repetition period           | No register control                                          | _                    |

| t <sub>1</sub>                                   | Start of sample LED2 pulse                 | Sample LED2 start count (bits 15-0 of register 01h)          | 4800                 |

| t <sub>2</sub>                                   | End of sample LED2 pulse                   | Sample LED2 end count (bits 15-0 of register 02h)            | 6399                 |

| t <sub>3</sub>                                   | Start of LED2 pulse                        | LED2 start count (bits 15-0 of register 03h)                 | 4800                 |

| t <sub>4</sub>                                   | End of LED2 pulse                          | LED2 end count (bits 15-0 of register 04h)                   | 6399                 |

| t <sub>5</sub>                                   | Start of sample LED2 ambient pulse         | Sample ambient LED2 start count (bits 15-0 of register 05h)  | 0                    |

| t <sub>6</sub>                                   | End of sample LED2 ambient pulse           | Sample ambient LED2 end count (bits 15-0 of register 06h)    | 1599                 |

| t <sub>7</sub>                                   | Start of sample LED1 pulse                 | Sample LED1 start count (bits 15-0 of register 07h)          | 1600                 |

| t <sub>8</sub>                                   | End of sample LED1 pulse                   | Sample LED1 end count (bits 15-0 of register 08h)            | 3199                 |

| t <sub>9</sub>                                   | Start of LED1 pulse                        | LED1 start count (bits 15-0 of register 09h)                 | 1600                 |

| t <sub>10</sub>                                  | End of LED1 pulse                          | LED1 end count (bits 15-0 of register 0Ah)                   | 3199                 |

| t <sub>11</sub>                                  | Start of sample LED1 ambient pulse         | Sample ambient LED1 start count (bits 15-0 of register 0Bh)  | 3200                 |

| t <sub>12</sub>                                  | End of sample LED1 ambient pulse           | Sample ambient LED1 end count (bits 15-0 of register 0Ch)    | 4700                 |

| t <sub>13</sub>                                  | Start of convert LED2 pulse                | LED2 convert start count (bits 15-0 of register 0Dh)         | 0                    |

| t <sub>14</sub>                                  | End of convert LED2 pulse                  | LED2 convert end count (bits 15-0 of register 0Eh)           | 1599                 |

| t <sub>15</sub>                                  | Start of convert LED2 ambient pulse        | LED2 ambient convert start count (bits 15-0 of register 0Fh) | 1600                 |

| t <sub>16</sub>                                  | End of convert LED2 ambient pulse          | LED2 ambient convert end count (bits 15-0 of register 10h)   | 3199                 |

| t <sub>17</sub>                                  | Start of convert LED1 pulse                | LED1 convert start count (bits 15-0 of register 11h)         | 3200                 |

| t <sub>18</sub>                                  | End of convert LED1 pulse                  | LED1 convert end count (bits 15-0 of register 12h)           | 4799                 |

| t <sub>19</sub>                                  | Start of convert LED1 ambient pulse        | LED1 ambient convert start count (bits 15-0 of register 13h) | 4800                 |

| t <sub>20</sub>                                  | End of convert LED1 ambient pulse          | LED1 ambient convert end count (bits 15-0 of register 14h)   | 6399                 |

| t <sub>21</sub>                                  | Start of first ADC conversion reset pulse  | ADC reset 0 start count (bits 15-0 of register 15h)          | 0                    |

| t <sub>22</sub>                                  | End of first ADC conversion reset pulse    | ADC reset 0 end count (bits 15-0 of register 16h)            | 0                    |

| t <sub>23</sub>                                  | Start of second ADC conversion reset pulse | ADC reset 1 start count (bits 15-0 of register 17h)          | 1600                 |

| t <sub>24</sub>                                  | End of second ADC conversion reset pulse   | ADC reset 0 end count (bits 15-0 of register 18h)            | 1600                 |

| t <sub>25</sub>                                  | Start of third ADC conversion reset pulse  | ADC reset 2 start count (bits 15-0 of register 19h)          | 3200                 |

| t <sub>26</sub>                                  | End of third ADC conversion reset pulse    | ADC reset 0 end count (bits 15-0 of register 1Ah)            | 3200                 |

| t <sub>27</sub>                                  | Start of fourth ADC conversion reset pulse | ADC reset 3 start count (bits 15-0 of register 1Bh)          | 4800                 |

| t <sub>28</sub>                                  | End of fourth ADC conversion reset pulse   | ADC reset 0 end count (bits 15-0 of register 1Ch)            | 4800                 |

| t <sub>29</sub>                                  | End of pulse repetition period             | Pulse repetition period count (bits 15-0 of register 1Dh)    | 6399                 |

## Table 2. Clock Edge Mapping to SPI Registers

(1) RED = LED2, IR = LED1.

SBAS602B – DECEMBER 2012 – REVISED FEBRUARY 2013

(1) RED = LED2, IR = LED1.

Figure 36. Relationship Between the ADC Reset and ADC Conversion Signals

AFE4490

www.ti.com

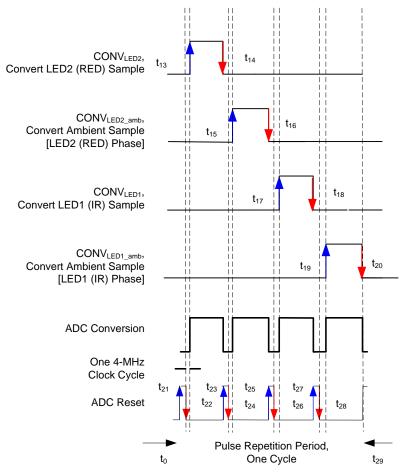

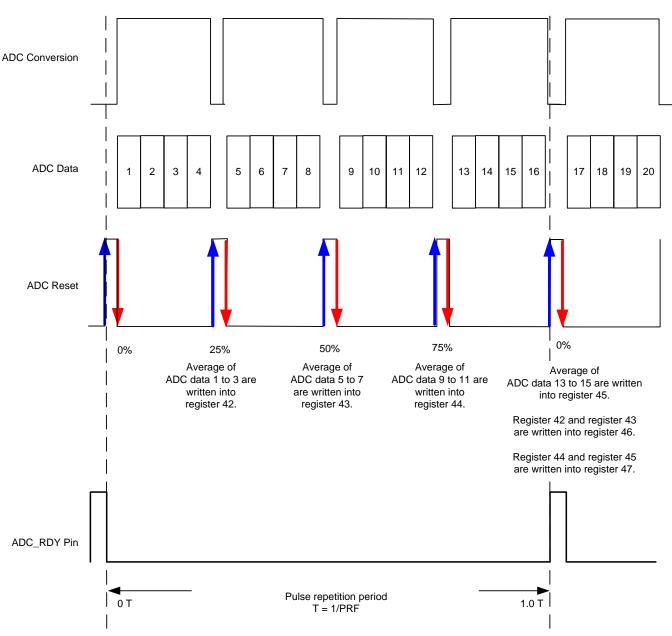

## ADC OPERATION AND AVERAGING MODULE

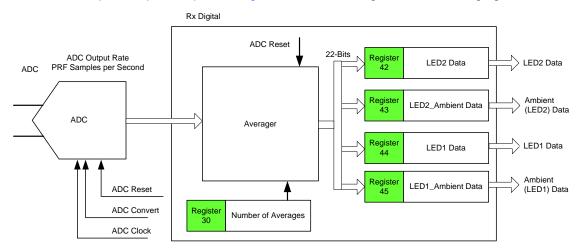

The ADC reset signal must be positioned at 25% intervals of the pulse repetition period (that is, 0%, 25%, 50%, and 75%). After the falling edge of the ADC reset signal, the ADC conversion phase starts. Each ADC conversion takes 50  $\mu$ s.

There are two modes of operation: without averaging and with averaging. The averaging mode can average multiple ADC samples and reduce noise to improve dynamic range because the ADC conversion time is usually shorter than 25% of the pulse repetition period. Figure 37 shows a diagram of the averaging module.

Figure 37. Averaging Module

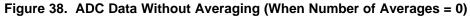

## **Operation Without Averaging**

In this mode, the ADC outputs a digital sample one time for every 50  $\mu$ s. At the next rising edge of the ADC reset signal, the first 22-bit conversion value is written into the result registers sequentially as follows (see Figure 38):

- At the 25% reset signal, the first 22-bit ADC sample is written to register 2Ah.

- At the 50% reset signal, the first 22-bit ADC sample is written to register 2Bh.

- At the 75% reset signal, the first 22-bit ADC sample is written to register 2Ch.

- At the next 0% reset signal, the first 22-bit ADC sample is written to register 2Dh. The contents of registers 2Ah and 2Bh are written to register 2Eh and the contents of registers 2Ch and 2Dh are written to register 2Fh.

At the rising edge of the ADC\_RDY signal, the contents of all six result registers can be read out.

## **Operation With Averaging**

In this mode, all ADC digital samples are accumulated and averaged after every 50  $\mu$ s. At the next rising edge of the ADC reset signal, the average value (22-bit) is written into the output registers sequentially as follows (see Figure 39):

- At the 25% reset signal, the averaged 22-bit word is written to register 2Ah.

- At the 50% reset signal, the averaged 22-bit word is written to register 2Bh.

- At the 75% reset signal, the averaged 22-bit word is written to register 2Ch.

- At the next 0% reset signal, the averaged 22-bit word is written to register 2Dh. The contents of registers 2Ah and 2Bh are written to register 2Eh and the contents of registers 2Ch and 2Dh are written to register 2Fh.

At the rising edge of the ADC\_RDY signal, the contents of all six result registers can be read out.

NSTRUMENTS

www.ti.com

ÈXAS

SBAS602B-DECEMBER 2012-REVISED FEBRUARY 2013

The number of samples to be used per conversion phase is specified in the CONTROL1 register (NUMAV[7:0]). The user must specify the correct value for the number of averages, as described in Equation 3:

NUMAV[7:0] + 1 =

$$\frac{0.25 \times \text{Pulse Repetition Period}}{50 \ \mu\text{s}}$$

(3)

When the number of averages is '0', the averaging is disabled and only one ADC sample is written to the result registers.

Note that he number of average conversions is limited by 25% of the PRF. For example, eight samples can be averaged with PRF = 625 Hz, and four samples can be averaged with PRF = 1250 Hz.

NOTE: Example is with three averages. The value of the NUMAVG[7:0] register bits = 2.

## Figure 39. ADC Data with Averaging Enabled

TEXAS INSTRUMENTS

SBAS602B - DECEMBER 2012 - REVISED FEBRUARY 2013

www.ti.com

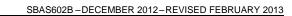

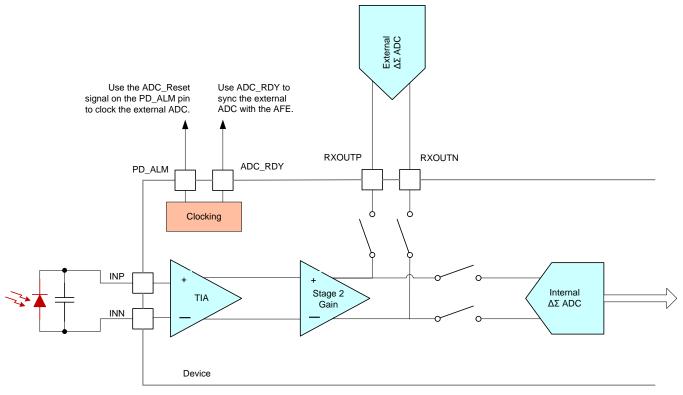

# AFE ANALOG OUTPUT MODE (ADC Bypass Mode)

The ADC bypass mode brings out the analog output voltage of the receiver front-end on two pins (RXOUTP, RXOUTN), around a common-mode voltage of approximately 0.9 V. In this mode, the internal ADC of the AFE4490 is disabled. Figure 40 shows a block diagram of this mode.

Figure 40. AFE4490 Set to ADC Bypass Mode

In ADC bypass mode, one of the internal clocks (ADC\_Reset) can be brought out on the PD\_ALM pin, as shown in Figure 41. This signal can be used to convert each of the four phases (within every pulse repetition period). Additionally, the ADC\_RDY signal can be used to synchronize the external ADC with the AFE. See Figure 42 for the timing of this mode.

Figure 41. AFE4490 in ADC Bypass Mode with ADC\_Reset to PD\_ALM Pin

www.ti.com

NOTE: RED = LED2, IR = LED1.

### Figure 42. AFE4490 Analog Output Mode (ADC Bypass) Timing Diagram

In ADC bypass mode, the ADC reset signal can be used to start conversions with the external ADC. Use registers 15h through 1Ch to position the ADC reset signal edges appropriately. Also, use the EN\_RSTCLK on the PD\_ALM pin register bit to bring out the ADC reset signal to the PD\_ALM pin. ADC\_RDY can be used to indicate the start of the pulse repetition period to the external ADC.

www.ti.com

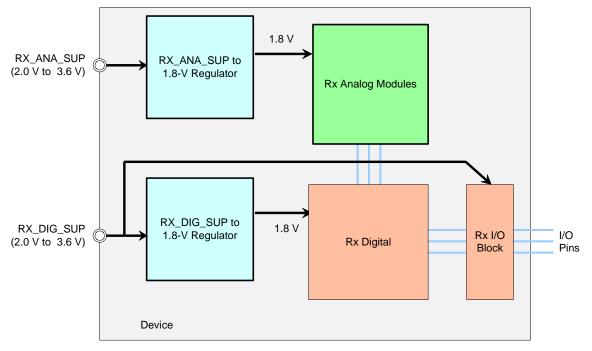

## **RECEIVER SUBSYSTEM POWER PATH**

The block diagram in Figure 43 shows the AFE4490 Rx subsystem power routing.

## Figure 43. Receive Subsystem Power Routing

AFE4490

#### www.ti.com

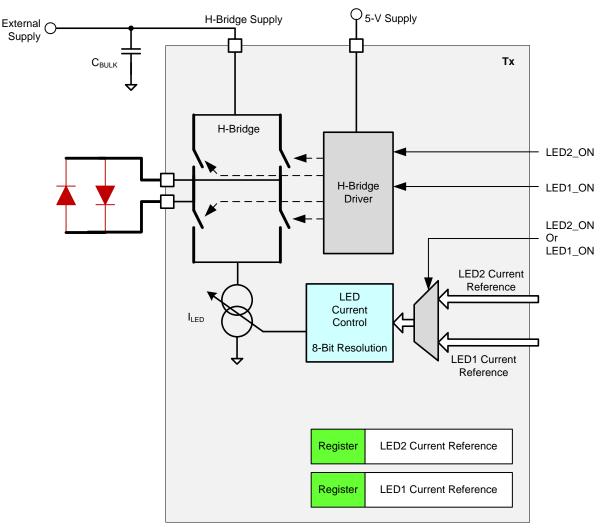

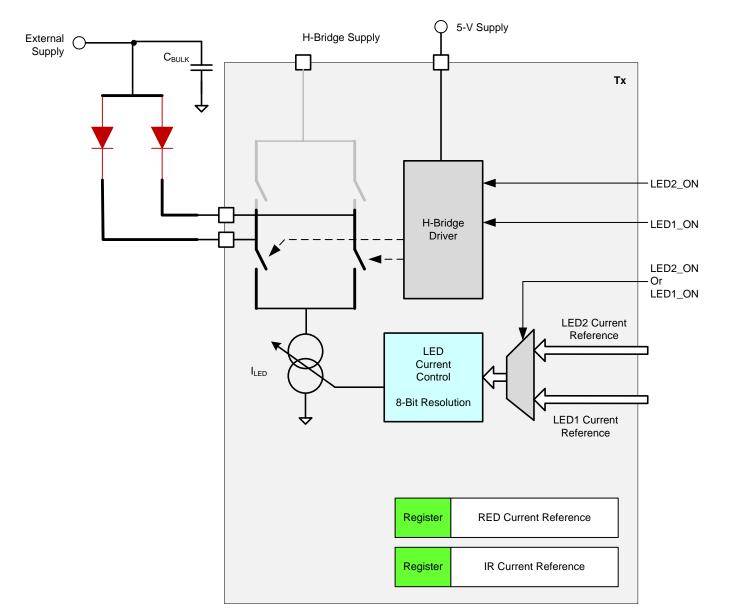

## **TRANSMIT SECTION**

The transmit section integrates the LED driver and the LED current control section with 8-bit resolution. This integration is designed to meet the specified dynamic range (based on a 1-sigma LED current noise).

The LED2 and LED1 reference currents can be independently set. The current source ( $I_{LED}$ ) locally regulates and ensures that the actual LED current tracks the specified reference.

Two LED driver schemes are supported:

- An H-bridge drive for a two-terminal back-to-back LED package, as shown in Figure 44. The minimum Hbridge supply voltage must be 2.5 V + (maximum voltage drop across the LED).

- A push-pull drive for a three-terminal LED package; see Figure 45. The minimum external supply voltage = 2.0 V + (maximum voltage drop across the LED). This value is the nominal value and depends on the registry LED current settings (refer to the LED\_RANGE[1:0] bits in the LEDCNTRL register).

Figure 44. Transmit: H-Bridge Drive

34

Submit Documentation Feedback

SBAS602B – DECEMBER 2012 – REVISED FEBRUARY 2013

Copyright © 2012–2013, Texas Instruments Incorporated

Figure 45. Transmit: Push-Pull LED Drive for Common Anode LED Configuration

SBAS602B-DECEMBER 2012-REVISED FEBRUARY 2013

## **Transmitter Power Path**

TX\_CTRL\_SUP\_5V Tx Reference and Control LED\_DRV\_SUP\_5V Tx LED Bridge Device

The block diagram in Figure 46 shows the AFE4490 Tx subsystem power routing.

Figure 46. Transmit Subsystem Power Routing

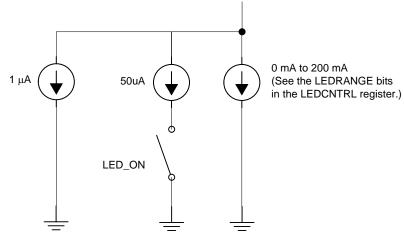

## LED Power Reduction During Periods of Inactivity

The diagram in Figure 47 shows how LED bias current passes 50 µA whenever LED\_ON occurs. In order to minimize power consumption in periods of inactivity, the LED\_ON control must be turned off.

Figure 47. LED Bias Current

## Texas Instruments

# DIAGNOSTICS

The device includes diagnostics to detect open or short conditions of the LED and photosensor, LED current profile feedback, and cable on or off detection.

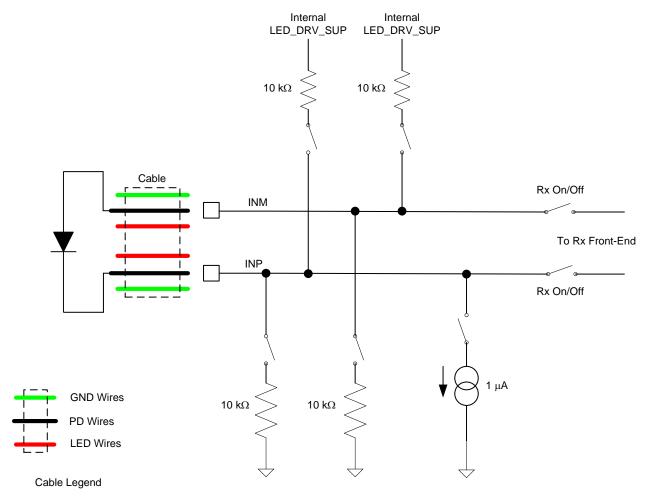

## Photodiode-Side Fault Detection

Figure 48 shows the diagnostic for the photodiode-side fault detection.

# SBAS602B - DECEMBER 2012 - REVISED FEBRUARY 2013

# www.ti.com

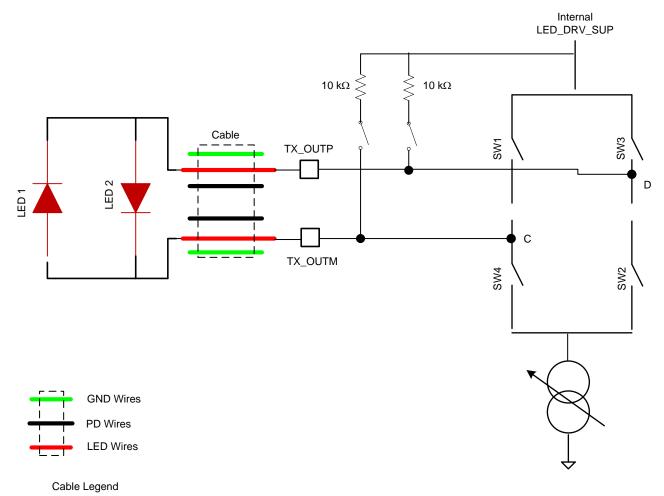

# **Transmitter-Side Fault Detection**

Figure 49 shows the diagnostic for the transmitter-side fault detection.

# **Diagnostics Module**

The diagnostics module, when enabled, checks for nine types of faults sequentially. The results of all faults are latched in 11 separate flags. At the end of the sequence, the state of the 11 flags are combined to generate two interrupt signals: PD\_ALM for photodiode-related faults and LED\_ALM for transmit-related faults. The status of all flags can also be read using the SPI interface. Table 3 details each fault and flag used. Note that the diagnostics module requires all AFE blocks to be enabled in order to function reliably.

| MODULE | SEQ. | FAULT                                   | FLAG1 | FLAG2 | FLAG3 | FLAG4 | FLAG5 | FLAG6 | FLAG7 | FLAG8 | FLAG9 | FLAG10 | FLAG11 |

|--------|------|-----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|

| _      | _    | No fault                                | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0      | 0      |

|        | 1    | Rx INP cable<br>shorted to LED cable    | 1     |       |       |       |       |       |       |       |       |        |        |

|        | 2    | Rx INM cable shorted to LED cable       |       | 1     |       |       |       |       |       |       |       |        |        |

| PD     | 3    | Rx INP cable<br>shorted to GND<br>cable |       |       | 1     |       |       |       |       |       |       |        |        |

|        | 4    | Rx INM cable<br>shorted to GND<br>cable |       |       |       | 1     |       |       |       |       |       |        |        |

|        | 5    | PD open or shorted                      |       |       |       |       | 1     | 1     |       |       |       |        |        |

|        | 6    | Tx OUTM line<br>shorted to GND<br>cable |       |       |       |       |       |       | 1     |       |       |        |        |

| LED    | 7    | Tx OUTP line<br>shorted to GND<br>cable |       |       |       |       |       |       |       | 1     |       |        |        |

|        | 8    | LED open or shorted                     |       |       |       |       |       |       |       |       | 1     | 1      |        |

|        | 9    | LED open or shorted                     |       |       |       |       |       |       |       |       |       |        | 1      |

# Table 3. Fault and Flag Diagnostics<sup>(1)</sup>

(1) Resistances below 10 k $\Omega$  are considered to be shorted.

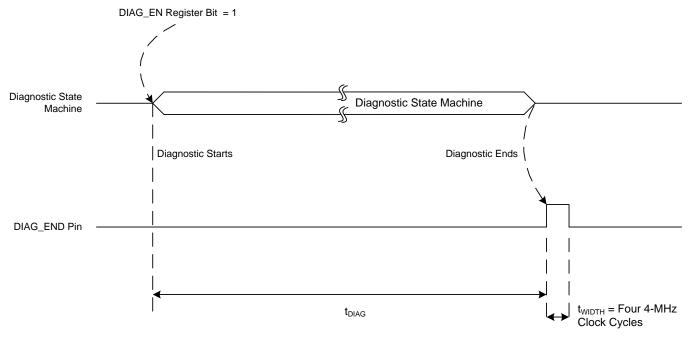

Figure 50 shows the timing for the diagnostic function.

# Figure 50. Diagnostic Timing Diagram